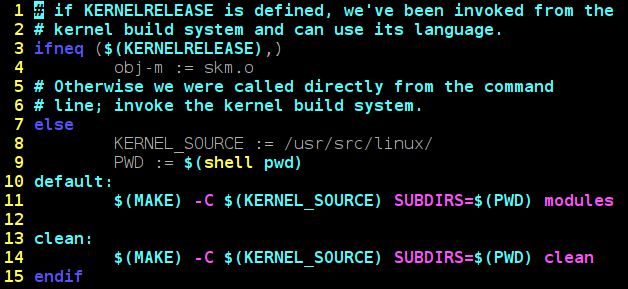

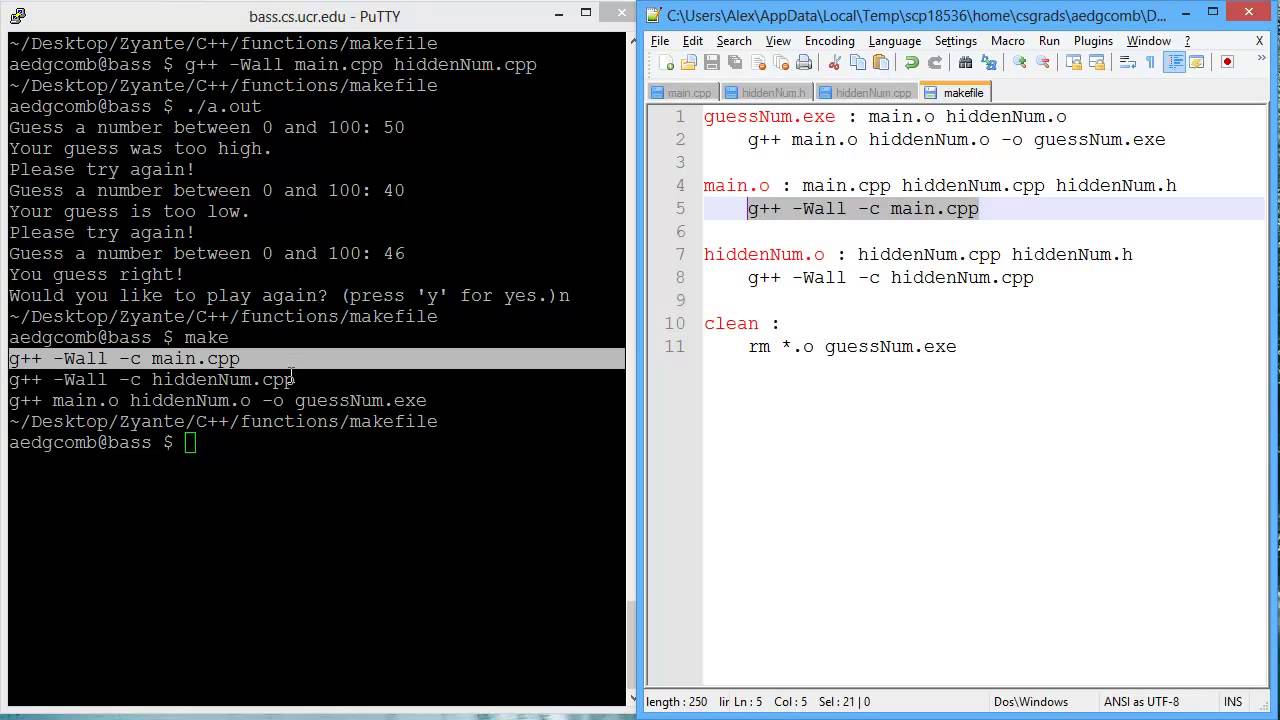

If the dependency file is newer than target file, target execute otherwise not execute. => When a target is a file-name, make compares the time-stamps of the target file and its dependency files. => Before executing the commands of corresponding target, its dependencies must be met, when they are not met, the targets of those dependencies are executed before the given make target, to supply the missing dependencies. Second and third target is main.o and function.o respectively which have dependencies of main.c and function.c respectively. Here our first and default target is “all” which looks for main.o and function.o file dependencies. And if they exist, whether they are newer than the target itself, by comparing file timestamps. => Based on make target specified in makefile, make checks if the dependency files of that target exist. If you have several Makefiles, then you can execute specific with the command:

=> When the make command is executed on terminal, it looks for a file named makefile or Makefile in the current directory and constructs a dependency tree.

Makefile for c program in linux manual#

The following are the manual steps to compile the project and produce the target gcc -c -I.

Makefile for c program in linux code#

function.c function.h and main.c to compile and generate binary, this is the simple way to compile your code rather than write compilation line on terminal again and again. And after the end of this small course you can write and understand Makefile easily.įor example if you have three files. Now writing Makefiles, But before that i want to tell you that i have divided this course in different levels so you can start slow with level 1 and go on. => For a large project, when a few changes are made to the source, manually recompiling the entire project each time is tedious, error-prone and time-consuming.

=> An important feature is that when a project is recompiled after a few changes, it will recompile only those files which are changed, and any other files that are dependent on it. It can be used to compile whole project in well arranged manner and generate your target according to your make rule(which we will discuss later) by entering single command that is make. => Large projects can contain multiple source files which are dependent in one another or arranged in hierarchical manner for example, in order to compile file A, you have to first compile B in order to compile B, you have to first compile C and so on.

In simple words, makefile will compile your source code in simple & fast way. Makefile is a script written in a certain prescribed syntax which helps to build the target output (normally, one or more executables) from source files by compilation and linking.

0 kommentar(er)

0 kommentar(er)